【1】海思MIPI接口学习

知识介绍

1.1 MIPI与LVDS知识点

- 了解MIPI与LVDS是什么。

- 了解MIPI与LVDS的相关协议

- 了解MIPI与LVDS的协议内容

1.2 MIPI与LVDS 相关简介

MIPI与LVDS简介

MIPI联盟下面针对不同硬件设备定义了不同的硬件设备内部接口,摄像头串行接口CSI2,显示串行接口DSI,射频接口DigRF,麦克风/喇叭接口SLIMbus等。

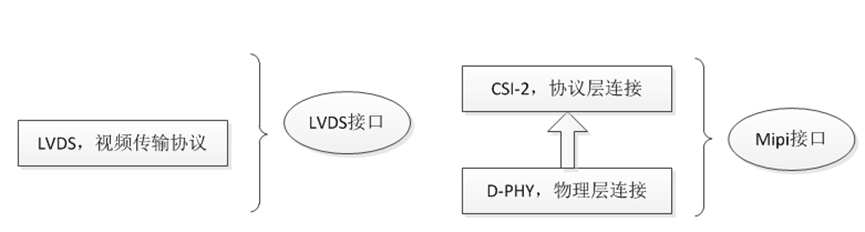

其中海思支持MIPI为MIPI Rx。MIPI规范由不同的工作组负责开发和维护,涵盖了不同的应用需求,分别面向不同领域的应用。MIPI Rx支持D-PHY和CSI-2(Camera Serial Interface)。D-PHY规定了物理层传输规范,CSI-2规定了Camera输出数据包的格式和协议。

(1)D-PHY

D-PHY是MIPI联盟发布的高速物理层标准,规定了主机和外设的物理层的物理特性及传输协议。D-PHY采用200mV源同步的低压差分信令技术,每个通道的频率范围为80MHz~1GHz。一般每路时钟最多可支持4个数据通道,4个通道共可以达到4Gbps的传输速率。D-PHY可以工作在低功耗(Low Power, LP)和高速(High Speed, HS)两种模式下。

(2)CSI-2

CSI-2是针对摄像头的数据协议,规定了主机与外设通信的数据包格式。

CSI-2可以支持不同像素格式的图像应用,数据传输的最小粒度是字节。为增加CSI-2性能,可以选择数据通道的数量,CSI-2协议规定了发送端将像素数据打包成字节的机制,并指明多个数据通道分配和管理的方式。字节数据以数据包的形式组织,数据包在SoT和EoT之间传输。接收端根据协议解析相应的数据包,恢复出原始的像素数据。

MIPI Rx支持RAW10/RAW12/RAW14格式的像素数据解析。

Figure 1 CSI-2 传输机制

海思支持的MIPI协议包

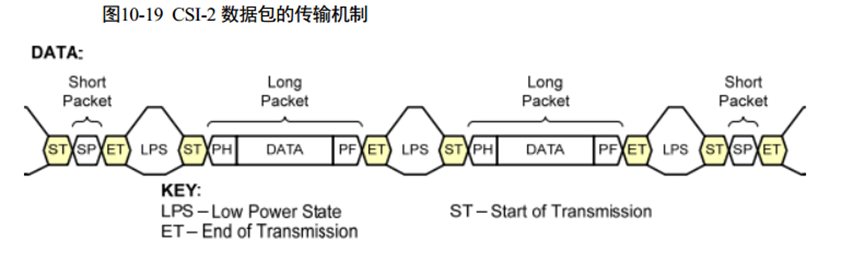

CSI-2的数据包分为长包和短包两种,包含有校验码,能进行误码纠正和错误检测。长包和短包都是在SoT和EoT之间传输,在数据传送的间隙,D-PHY处于LP模式。CSI-2数据包的传输机制如图10-19所示。PH和PF分别表示Packet Header和Packet Footer。

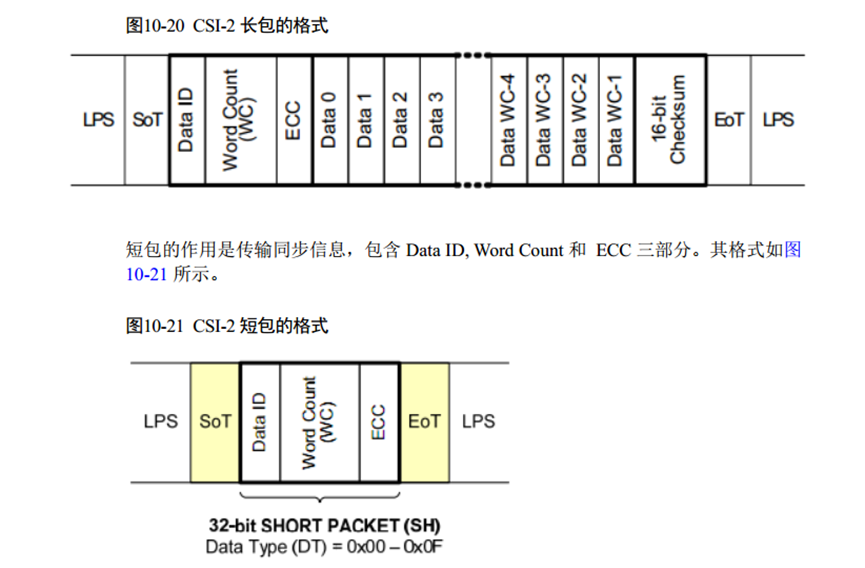

长包用于传输有效像素数据,分为五部分:Data ID, Word Count, ECC, PAYLOAD, Checksum。

Data ID包含Virtual Channel和Data Type。Virtual Channel控制传输所用的通道,可以指定通道的复用,让不同的通道传输不同的数据。Data Type指定数据的类型。

Word Count指示接收端需要接收到的数据量。

ECC是8位纠错码,可以纠正或检测Data Type和Word Count的误码。

Payload Data是需要传输的像素数据。

Checksum是利用线性反馈移位寄存器产生的校验和,用于Payload数据的校验。长包的结构如图图10-20所示。

海思的mipi与LVDS

海思视频层关于mipi可以分为如下:

海思所支持的MIPI Rx是一个支持多种差分视频输入接口的采集单元,通过combo-PHY接收MIPI/LVDS/sub-LVDS/HiSPi/DC接口的数据,通过不同的功能模式配置,MIPI Rx可以支持多种速度和分辨率的数据传输需求,支持多种外部输入设备。MIPI Rx最大支持1Link/4Lane MIPI输入、1Link/4Lane或2Link/8Lane LVDS输入以上输入。管脚可复用为单端DC/BT.1120通道输入,从而可以用更少的芯片管脚提供更好的兼容性。

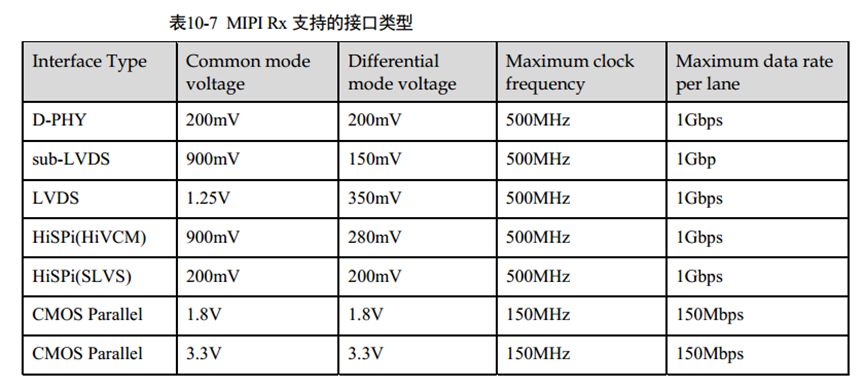

海思的mip接口与LVDS接口是兼容的!硬件通过配置不同的共模电压和差分电路,可以选择相应的MIPI者LVDS接口,支持接口如下所示:

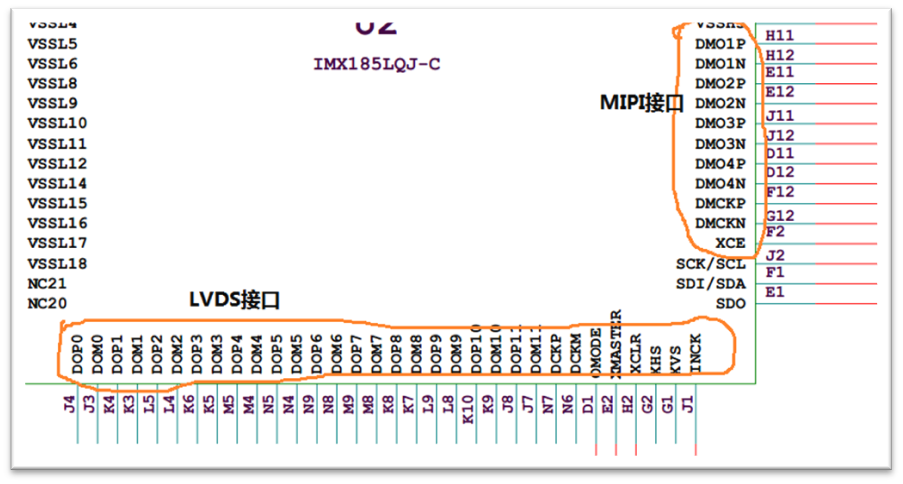

具体是使用LVDS还是MIPI接口,根据硬件电路来确定,也就是根据我们自身硬件选择,有些芯片支持LVDS与MIPI两种接口,有些芯片不支持,具体需要查看芯片自身。一般来说,在硬件电路中,LVDS的接口使用名称叫做DOPX/DOMX,而MIPI的接口一般为DMOXP/DMOXN,以IMX185来说,硬件抽象接口如下:

实际配置如下:

底部的DOP0与DOM0等接口为LVDS接口,DMOXN/DMOXP为MIPI接口,以实际需求为准。